IP

IP cores

Bao Nguyen’s silicon-proven IP provides designers with a broad range of synthesizable implementation IP, hardened PHYs and verification IP for ASIC, FPGA, and SoC designs. The Bao Nguyen in-house IP portfolio includes bus interface, mixed signal, data converter, multimedia, power management, and SERDES.

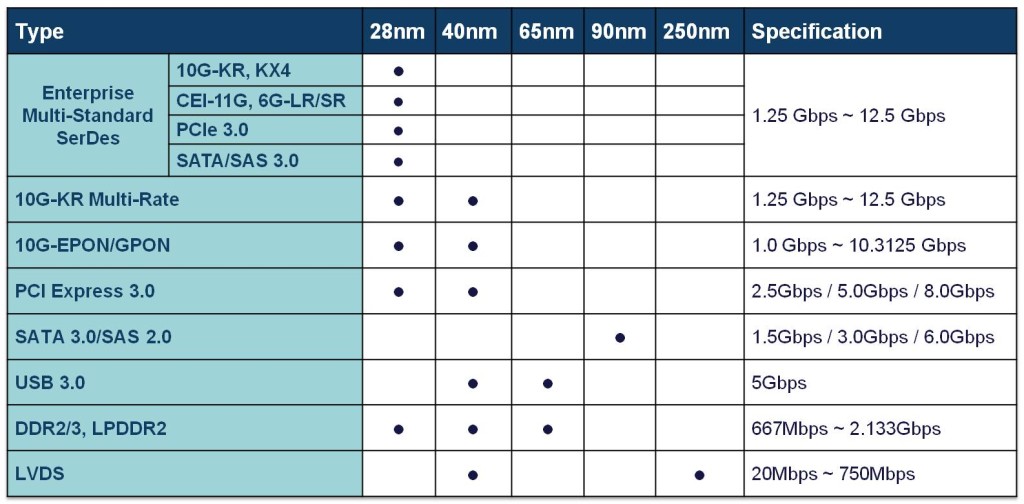

- Bus Interface IP includes digital and mixed-signal standards-based connectivity IP such as 1G and 10G SerDes (supporting GPON/EPON applications as well as XFI and 10G BASE-KR back plane applications), PCI-e 3.0/2.0, SATA 3.0/2.0/1.0, SAS 2/1, USB3.0/2.0/1.0, HDMI V1.4 TX and RX, Interlaken/Double XAUI, XAUI, SGMII, SRIO, Fiber Channel, AHB/AXI, and Ethernet.

- Data Converter IP includes SAR and pipelined ADCs and wide bandwidth, precision and high speed DACs.

- Mixed-Signal IP includes LVDS, power management, DC-DC converters, clock generator IP, 3.3V/2.5V high voltage tolerant/drive I/O, etc.

- Memory Element IP includes many offerings from TSMC including single- and dual-port memory compilers and memory types are also available.

-

Peripheral Core IP includes DDR2/3 Controller and PHY IP up to 1600Mbps silicon-proven IP (next generation targeting 2133Mbps) with both wire bond and flip chip solutions.

- Processor IP includes MCU/MPU and hardened ARM processor cores including an ARM development platform for quick prototyping.

These IPs are silicon and production proven in the ASIC projects of a global customer base.

Bao Nguyen’s wide experience with all kinds of IP combined with a comprehensive customization flexibility allows customers to quickly meet both product requirements and to achieve market goals at the same time. Bao Nguyen has an established reputation in integrating a wide range of IP supported by a full suite of design services and an experienced technical team dedicated to developing design flows that address the complexities of today’s ASIC designs.

Analog IP

High Speed Interface IP